# The WaveScalar Architecture

STEVEN SWANSON, ANDREW SCHWERIN, MARTHA MERCALDI, ANDREW PETERSEN, ANDREW PUTNAM, KEN MICHELSON, MARK OSKIN, and SUSAN J. EGGERS

University of Washington

Silicon technology will continue to provide an exponential increase in the availability of raw transistors. Effectively translating this resource into application performance, however, is an open challenge that conventional superscalar designs will not be able to meet. We present WaveScalar as a scalable alternative to conventional designs. WaveScalar is a dataflow instruction set and execution model designed for scalable, low-complexity/high-performance processors. Unlike previous dataflow machines, WaveScalar can efficiently provide the sequential memory semantics that imperative languages require. To allow programmers to easily express parallelism, WaveScalar supports pthread-style, coarse-grain multithreading and dataflow-style, fine-grain threading. In addition, it permits blending the two styles within an application, or even a single function.

To execute WaveScalar programs, we have designed a scalable, tile-based processor architecture called the WaveCache. As a program executes, the WaveCache maps the program's instructions onto its array of processing elements (PEs). The instructions remain at their processing elements for many invocations, and as the working set of instructions changes, the WaveCache removes unused instructions and maps new ones in their place. The instructions communicate directly with one another over a scalable, hierarchical on-chip interconnect, obviating the need for long wires and broadcast communication.

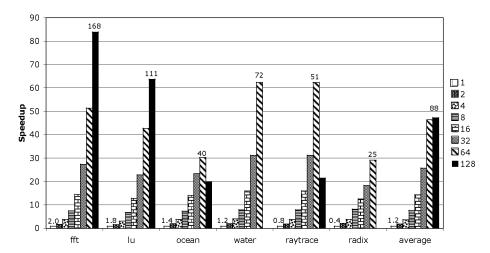

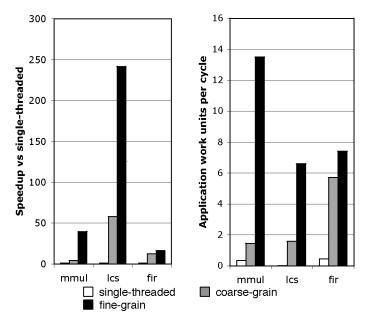

This article presents the WaveScalar instruction set and evaluates a simulated implementation based on current technology. For single-threaded applications, the WaveCache achieves performance on par with conventional processors, but in less area. For coarse-grain threaded applications the WaveCache achieves nearly linear speedup with up to 64 threads and can sustain 7–14 multiply-accumulates per cycle on fine-grain threaded versions of well-known kernels. Finally, we apply both styles of threading to equake from Spec2000 and speed it up by 9x compared to the serial version.

Categories and Subject Descriptors: C.1.3 [**Processor Architectures**]: Other Architecture Styles—*Data-flow architectures*; C.5.0 [**Computer System Implementation**]: General; D.4.1 [**Operating Systems**]: Process Management—*Threads, concurrency*

General Terms: Performance, Experimentation, Design

Additional Key Words and Phrases: WaveScalar, dataflow computing, multithreading

Authors' address: S. Swanson (contact author), A. Schwerin, M. Mercaldi, A. Petersen, A. Putnam, K. Michelson, M. Oskin, and S. J. Eggers, Department of Computer Science and Engineering, Allen Center for CSE, University of Washington, Box 352350, Seattle, WA 98195; email: swanson@cs.ucsd.edu

Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or direct commercial advantage and that copies show this notice on the first page or initial screen of a display along with the full citation. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, to republish, to post on servers, to redistribute to lists, or to use any component of this work in other works requires prior specific permission and/or a fee. Permissions may be requested from Publications Dept., ACM, Inc., 2 Penn Plaza, Suite 701, New York, NY 10121-0701 USA, fax +1 (212) 869-0481, or permissions@acm.org. © 2007 ACM 0738-2071/2007/05-ART4 \$5.00 DOI 10.1145/1233307.1233308 http://doi.acm.org/10.1145/1233307.1233308

#### **ACM Reference Format:**

Swanson, S., Schwerin, A., Mercaldi, M., Petersen, A., Putnam, A., Michelson, K., Oskin, M., and Eggers, S. J. 2007. The WaveScalar architecture. ACM Trans. Comput. Syst. 25, 2, Article 4 (May 2007), 54 pages. DOI = 10.1145/1233307.1233308 http://doi.acm.org/10.1145/1233307.1233308

#### 1. INTRODUCTION

It is widely accepted that Moore's Law will hold for the next decade. However, although more transistors will be available, simply scaling-up current architectures will not convert them into commensurate increases in performance [Agarwal et al. 2000]. This resulting gap between the increases in performance we have come to expect and those that larger versions of existing architectures will be able to deliver will force engineers to search for more scalable processor architectures.

Three problems contribute to this gap: (1) the ever-increasing disparity between computation and communication performance, specifically, fast transistors but slow wires; (2) the increasing cost of circuit complexity, leading to longer design times, schedule slips, and more processor bugs; and (3) the decreasing reliability of circuit technology caused by shrinking feature sizes and continued scaling of the underlying material characteristics. In particular, modern superscalar processor designs will not scale because they are built atop a vast infrastructure of slow broadcast networks, associative searches, complex control logic, and centralized structures.

We propose a new instruction set architecture (ISA), called WaveScalar [Swanson et al. 2003], that addresses these challenges by building on the dataflow execution model [Dennis and Misunas 1975]. The dataflow execution model is well-suited to running on a decentralized, scalable processor because it is inherently decentralized. In this model, instructions execute when their inputs are available, and detecting this condition can be done locally for each instruction. The global coordination upon which the von Neumann model relies, in the form of a program counter, is not required. In addition, the dataflow model allows programmers and compilers to express parallelism explicitly, instead of relying on the underlying hardware (e.g., an out-of-order superscalar) to extract it.

WaveScalar exploits these properties of the dataflow model, and also addresses a long-standing deficiency of dataflow systems. Previous dataflow systems could not efficiently enforce the sequential memory semantics that imperative languages, such as C, C++, and Java, require. Instead, they used special dataflow languages that limited their usefulness. A recent *ISCA* keynote address [Arvind 2005] noted that if dataflow systems are to become a viable alternative to the von Neumann status quo, they must enforce sequentiality on memory operations without severely reducing parallelism among other instructions. WaveScalar addresses this challenge with a memory ordering scheme, called wave-ordered memory, that efficiently provides the memory ordering needed by imperative languages.

Using this memory ordering scheme, WaveScalar supports conventional single-threaded and pthread-style multithreaded applications. It also

efficiently supports fine-grain threads that can consist of only a handful of instructions. Programmers can combine these different thread models in the same program, or even in the same function. Our data shows that applying diverse styles of threading to a single program can expose significant parallelism in code that would otherwise be difficult to fully parallelize.

Exposing parallelism is only the first task. The processor must then translate this parallelism into performance. We exploit WaveScalar's decentralized dataflow execution model to design the *WaveCache*, a scalable, decentralized processor architecture for executing WaveScalar programs. The WaveCache has no central processing unit. Instead, it consists of a sea of processing nodes in a substrate that effectively replaces the central processor and instruction cache of a conventional system. The WaveCache loads instructions from memory and assigns them to processing elements for execution. The instructions remain at their processing elements for a large number, potentially millions, of invocations. As the working set of instructions for the application changes, the WaveCache evicts unneeded instructions and loads the necessary ones into vacant processing elements.

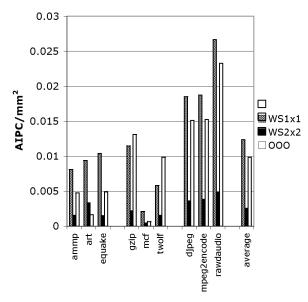

This article describes and evaluates the WaveScalar ISA and WaveCache architecture. First, we describe those aspects of WaveScalar's ISA and the Wave-Cache architecture that are required for executing single-threaded applications, including the wave-ordered memory interface. We evaluate the performance of a small, simulated WaveCache on several single-threaded applications. Our data demonstrates that this WaveCache performs comparably to a modern out-of-order superscalar design, but requires 20% less silicon area.

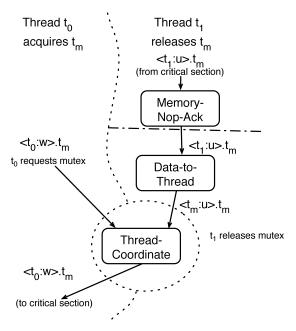

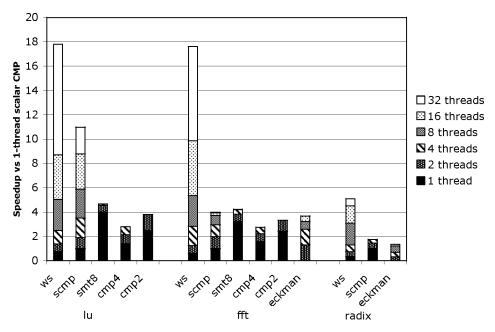

Next, we extend WaveScalar and the WaveCache to support conventional pthread-style threading. The changes to WaveScalar include lightweight dataflow synchronization primitives and support for multiple, independent sequences of wave-ordered memory operations. The multithreaded WaveCache achieves nearly linear speedup on the six Splash2 parallel benchmarks that we use.

Finally, we delve into WaveScalar's dataflow underpinnings, the advantages they provide, and how programs can combine them with conventional multithreading. We describe WaveScalar's "unordered" memory interface and show how it can be used with fine-grain threading to reveal substantial parallelism. Fully utilizing these techniques requires a custom compiler which is not yet complete, so we evaluate these two features by hand-coding three common kernels and rewriting part of the *equake* benchmark to use a combination of fine-and coarse-grain threading styles. The results demonstrate that these techniques speed-up the kernels by between 16 and 240 times and *equake* by a factor of 9, compared to the serial versions.

The rest of this article is organized as follows. Sections 2 and 3 describe the single-threaded WaveScalar ISA and WaveCache architecture, respectively. Section 4 then evaluates them. Section 5 describes WaveScalar's coarse-grain threading facilities and the changes to the WaveCache that support them. Section 6 presents WaveScalar's dataflow-based facilities that support fine-grain parallelism and illustrates how we can combine both threading styles to enhance performance. Finally, Section 7 concludes.

#### 2. SINGLE-THREADED WAVESCALAR

Although the dataflow model that WaveScalar uses is fundamentally different than the von Neumann model that dominates conventional designs, both models accomplish many of the same tasks in order to execute single-threaded programs written in conventional programming languages. For example, both must determine which instructions to execute and provide a facility for conditional execution; they must pass operands from one instruction to another and they must access memory.

For many of these tasks, WaveScalar borrows from previous dataflow machines. Its interface to memory, however, is unique and one of its primary contributions to dataflow computing. The WaveScalar memory interface provides an efficient method for encoding memory ordering information in a dataflow model, enabling efficient execution of programs written in imperative programming languages. Most earlier dataflow machines could not efficiently execute codes written in imperative languages because they could not easily enforce the memory semantics that these programs require.

To provide context for our description, we first describe how the von Neumann model accomplishes the tasks previously outlined and why the von Neumann model is inherently centralized. Then we describe how WaveScalar's model accomplishes the same goals in a decentralized manner and how WaveScalar's memory interface works. WaveScalar's decentralized execution model provides the basis for the decentralized, general-purpose hardware architecture presented in Section 3.

## 2.1 The von Neumann Model

Von Neumann processors represent programs as a list of instructions that reside in memory. A program counter (PC) selects instructions for execution by stepping from one memory address to the next, causing each instruction to execute in turn. Special instructions can modify the PC to implement conditional execution, function calls, and other types of control transfer.

In modern von Neumann processors, instructions communicate with one another by writing and reading values in the register file. After an instruction writes a value into the register file, all subsequent instructions that read the value are data-dependent on the writing instruction.

To access memory, programs issue load and store instructions. A key tenet of the von Neumann model is the set of memory semantics it provides in which loads and stores occur (or appear to occur) in the order in which the PC fetched them. Enforcing this order is required to preserve read-after-write, write-after-write, and write-after-read dependences between instructions. Modern imperative languages, such as C, C++, or Java, provide essentially identical memory semantics and rely on the von Neumann architecture's ability to implement these semantics efficiently.

At its heart, the von Neumann model describes execution as a linear centralized process. A single program counter guides execution and there is always exactly one instruction that, according to the model, should execute next. This is both a strength and a weakness. On one hand, it makes control transfer easy,

tightly bounds the amount of state that the processor must maintain, and provides a simple set of memory semantics. History has also demonstrated that constructing processors based on the model is feasible (and extremely profitable!). On the other hand, the model expresses no parallelism. While the performance of its processors has improved exponentially for over three decades, continued scalability is uncertain.

#### 2.2 WaveScalar's ISA

The dataflow execution model has no PC to guide instruction fetch and memory ordering and no register file to serve as a conduit of data values between dependent instructions. Instead, it views instructions as nodes in a dataflow graph, which only execute after they have received their input values. Memory operations execute in the same data-driven fashion, which may result in their being executed out of the program's linear order. However, although the model provides no total ordering of a program's instructions, it does enforce the partial orders that a program's dataflow graph defines. Since individual partial orders are data-independent, they can be executed in parallel, providing the dataflow model with an inherent means of expressing parallelism of arbitrary granularity. In particular, the granularity of parallelism is determined by the length of a data-dependent path. For all operations, data values are passed directly from producer to consumer instructions without intervening accesses to a register file.

Dataflow's advantages are its explicit expression of parallelism among dataflow paths and its decentralized execution model that obviates the need for a program counter or any other centralized structure to control instruction execution. However, these advantages do not come for free. Control transfer is more expensive in the dataflow model, and the lack of a total order on instruction execution makes it difficult to enforce the memory ordering that imperative languages require. WaveScalar handles control using the same technique as previous dataflow machines (described in Section 2.2.2), but overcomes the problem of memory access order with a novel architectural technique called wave-ordered memory [Swanson et al. 2003] (described in Section 2.2.5). Wave-ordered memory essentially creates a "chain" of dependent memory operations at the architectural level; the hardware then guarantees that the operations execute in the order the chain defines.

Next we describe the WaveScalar ISA in detail. Much of the information is not unique to WaveScalar and reflects its dataflow heritage. We present it here for completeness and to provide a thorough context for the discussion of memory ordering, which is WaveScalar's key contribution to dataflow instructions sets. Readers already familiar with dataflow execution could skim Sections 2.2.1, 2.2.2, and 2.2.4.

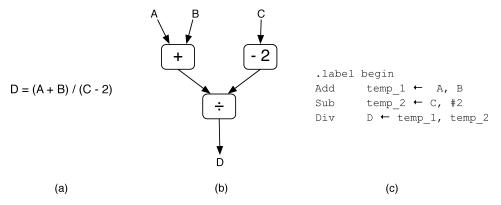

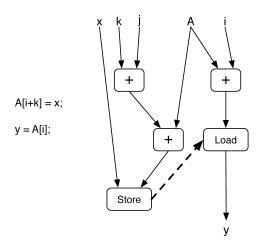

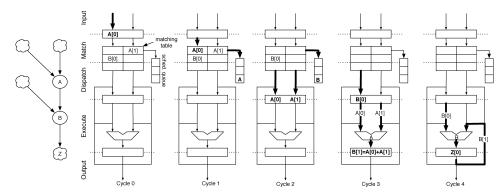

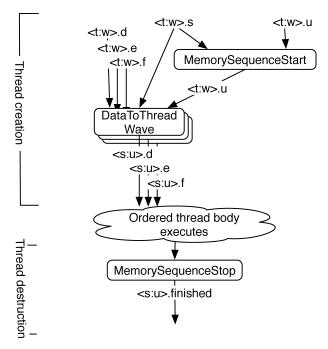

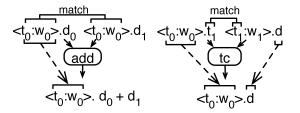

2.2.1 *Program Representation and Execution.* WaveScalar represents programs as dataflow graphs. Each node in the graph is an instruction, and the arcs between nodes encode static data dependences (i.e., dependences that are known to exist at compile time) between instructions. Figure 1 shows a simple

Fig. 1. A simple dataflow fragment: (a) a simple program statement; (b) its dataflow graph; and (c) the corresponding WaveScalar assembly. The order of the WaveScalar assembly statements is unimportant, since they will be executed in dataflow fashion.

piece of code, its corresponding dataflow graph, and the equivalent WaveScalar assembly language.

The mapping between the drawn graph and the dataflow assembly language is simple: Each line of assembly represents an instruction, and the arguments to the instructions are dataflow edges. Outputs precede the " $\leftarrow$ ". The assembly code resembles RISC-style assembly but differs in two key respects. First, although the dataflow edges syntactically resemble register names, they do not correspond to a specific architectural entity. Consequently, like pseudoregisters in a compiler's program representation, there can be an arbitrary number of them. Second, the order of instructions does not affect their execution, since they will be executed in dataflow fashion. Each instruction does have a unique address, however, used primarily for specifying function call targets (see Section 2.2.4). As in assembly languages for von Neumann machines, we can use labels (e.g., begin in the figure) to refer to specific instructions. We can also perform arithmetic on labels. For instance, begin +1 would be the Subtract instruction.

Unlike the PC-driven von Neumann model, execution of the dataflow graph is data-driven. Instructions execute according to the dataflow firing rule which stipulates that an instruction can fire at any time after values arrive on all of its inputs. Instructions send the values they produce along arcs in the program's dataflow graph to their consumer instructions, causing them to fire in turn. In Figure 1, once inputs A and B are ready, the ADD can fire and produce the lefthand input to the Divide. Likewise, once C is available, the Subtract computes the other input to the Divide instruction. The Divide then executes and produces D.

The dataflow firing rule is inherently decentralized because it allows each instruction to act autonomously, waiting for inputs to arrive and generating outputs. Portions of the dataflow graph that are not explicitly data-dependent do not communicate at all.

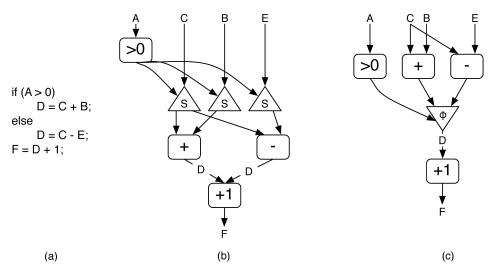

2.2.2 Control Flow. Dataflow's decentralized execution algorithm makes control transfers more difficult to implement. Instead of steering a single PC

Fig. 2. Implementing control in WaveScalar: (a) an IF-Then-Else construct and equivalent dataflow representations; (b) Steer instructions (triangles labeled "s") ensure that only one side of the branch executes, while (c) computes both sides and a  $\phi$  instruction selects the result to use.

through the executable so that the processor executes one path instead of the other, WaveScalar steers values into one part of the dataflow graph and prevents them from flowing into another. It can also use predication to perform both computations and later discard the results on the wrong path. In both cases, the dataflow graph must contain a control instruction for each live value, which is a source of some overhead in the form of extra static instructions.

WaveScalar uses Steer instructions to steer values to the correct path and  $\phi$  instructions for predication. The Steer [Culler et al. 1991] instruction takes an input value and a Boolean output selector. It directs the input to one of two possible outputs depending on the selector value, effectively steering data values to the instructions that should receive them. Figure 2(b) shows a simple conditional implemented with Steer instructions. Steer instructions correspond most directly to traditional branch instructions, and are required for implementing loops. In many cases a Steer instruction can be combined with a normal arithmetic operation. For example, ADD-AND-Steer takes three inputs, namely a predicate and two operands, and steers the result depending on the predicate. WaveScalar provides a steering version for all one- and two-input instructions.

The  $\phi$  instruction [Cytron et al. 1991] takes two input values and a Boolean selector input and, depending on the selector, passes one of the inputs to its output. Moreover,  $\phi$  instructions are analogous to conditional moves and provide a form of predication. They are desirable because they remove the selector input from the critical path of some computations and therefore increase parallelism. They are also wasteful, however, because they discard the unselected input. Figure 2(c) shows  $\phi$  instructions in action.

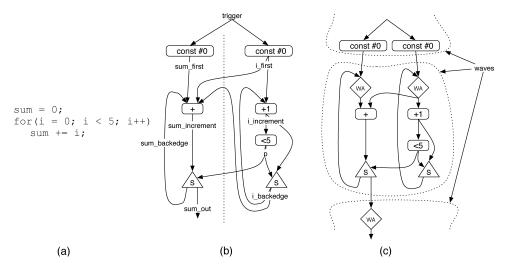

2.2.3 Loops and Waves. The Steer instruction may appear to be sufficient for WaveScalar to express loops, since it provides a basic branching facility.

Fig. 3. Loops in WaveScalar: (a) a simple loop; (b) a naive, slightly broken dataflow implementation; and (c) the correct WaveScalar implementation.

However, in addition to branching, dataflow machines must also distinguish dynamic instances of values from different iterations of a loop. Figure 3(a) shows a simple loop that illustrates both the problem and WaveScalar's solution.

Execution begins when data values arrive at the Const instructions, which inject zeros into the body of the loop, one for sum and one for i (Figure 3(b)). On each iteration through the loop, the left side updates sum and the right side increments i and checks whether it is less than 5. For the first five iterations  $(i=0\ldots 4)$ , p is true and the Steer instructions steer the new values for sum and i back into the loop. On the last iteration, p is false, and the final value of sum leaves the loop via the sum\_out edge. Since i is dead after the loop, the false output of the righthand-side Steer instruction produces no output.

The problem arises because the dataflow execution model makes no guarantee about how long it takes for a data value to flow along a given dataflow arc. If sum\_first takes a long time to reach the Add instruction, the right-side portion of the dataflow graph could run ahead of the left, generating multiple values on i\_backedge and p. How would the Add and Steer instructions on the left know which of these values to use? In this particular case, the compiler could solve the problem by unrolling the loop completely, but this is not always possible nor wise.

Previous dataflow machines provided one of two solutions. In the first, *static dataflow* [Dennis and Misunas 1975; Davis 1978], only one value is allowed on each arc at any time. In a static dataflow system, the dataflow graph as shown works fine. The processor would use back-pressure to prevent the Compare and Increment instructions from producing a new value before the old values had been consumed. While this restriction resolves the ambiguity between different value instances, it also reduces parallelism by preventing multiple iterations of a loop from executing simultaneously, and makes recursion difficult to support.

A second model, *dynamic dataflow* [Shimada et al. 1986; Gurd et al. 1985; Kishi et al. 1983; Grafe et al. 1989; Papadopoulos and Culler 1990], tags each data value with an identifier and allows multiple values to wait at the input to an instruction. The dataflow firing rule is modified so that an instruction fires only when tokens with matching tags are available on all of its inputs. The combination of a data value and its tag is called a *token*. WaveScalar is a dynamic dataflow architecture.

Dynamic dataflow architectures differ in how they manage and assign tags to values. In WaveScalar the tags are called  $wave\ numbers$  [Swanson et al. 2003]. We denote a WaveScalar token with wave number w and value v as w.v. Instead of assigning different wave numbers to different instances of specific instructions (as did most dynamic dataflow machines), WaveScalar assigns them to compiler-delineated portions of the dataflow graph, called waves. Waves are similar to hyperblocks [Mahlke et al. 1992], but are more general, since they can both contain control-flow joins and have more than one entrance. They cannot contain loops. Figure 3(c) shows the example loop divided into waves (as shown by dotted lines). At the top of each wave is a set of Wave-Advance instructions (small diamonds), each of which increments the wave number of the value that passes through it.

Assume that the code before the loop is wave number 0. When the code executes, the two Const instructions will produce 0.0 (wave number 0, value 0). The Wave-Advance instructions will take these as input and each will output 1.0, which will propagate through the body of the loop as before. At the end of the loop, the righthand-side Steer instruction will produce 1.1 and pass it back to Wave-Advance at the top of its side of the loop, which will then produce 2.1. A similar process takes place on the left side of the graph. After five iterations, the left Steer instruction produces the final value of sum: 5.10, which flows directly into Wave-Advance at the beginning of the follow-on wave. With the Wave-Advance instructions in place, the right side can run ahead safely, since instructions will only fire when the wave numbers in operand tags match. More generally, wave numbers allow instructions from different wave instances, in this case iterations, to execute simultaneously.

In addition to allowing WaveScalar to extract parallelism, wave numbers also play a key role in enforcing memory ordering (see Section 2.2.5).

2.2.4 Function Calls. Function calls on a von Neumann processor are fairly simple: The caller saves "caller saved" registers, pushes function arguments and the return address onto the stack (or stores them in specific registers), and then uses a jump instruction to set the PC to the address of the beginning of the called function, triggering its execution.

Being a dataflow architecture, WaveScalar must follow a slightly different convention. Since it has no registers, it does not need to preserve register values. It must, however, explicitly pass arguments and a return address to the

<sup>&</sup>lt;sup>1</sup>The execution model does not specify where the data values are stored nor how matching takes place. Efficiently storing and matching input tokens is a key challenge in dynamic dataflow architecture, and Section 3 discusses this.

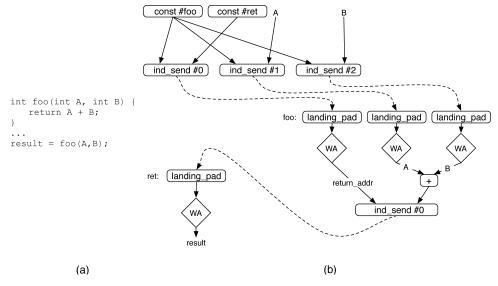

Fig. 4. A function call: (b) the dataflow graph for (a) a call to a simple function. The lefthand-side of the dataflow graph uses Indirect-Send instructions to call function foo on the right. The dashed lines show data dependences that WaveScalar must resolve at runtime. The immediate values on the trio of Indirect-Send instructions are offsets from the first instruction in foo.

function and trigger its execution. Passing arguments creates a data dependence between the caller and callee. For indirect functions, these dependences are not statically known and therefore the static dataflow graph of the application does not contain them. Instead, WaveScalar provides a mechanism to send a data value to an instruction at a computed address. The instruction that allows this is called Indirect-Send.

INDIRECT-SEND takes as input the data value to send, a base address for the destination instruction (usually a label), and the offset from that base (as an immediate). For instance, if the base address is 0x1000, and the offset is 4, INDIRECT-SEND sends the data value to the instruction at 0x1004.

Figure 4 contains the dataflow graph for a small function and a call site. Dashed lines in the graphs represent the dependences that exist only at runtime. The Landing-Pad instruction, as its name suggests, provides a target for a data value sent via Indirect-Send. To call the function, the caller uses three Indirect-Send instructions: two for the arguments A and B and one for the return address, which is the address of the return Landing-Pad (label ret in the figure). Another Indirect-Send is used to return from the function.

When the values arrive at foo, the Landing-Pad instructions pass them to Wave-Advance instructions that, in turn, forward them into the function body (the callee immediately begins a new wave). Once the function is finished, perhaps having executed many waves, foo uses a single Indirect-Send to return the result to the caller's Landing-Pad instruction. After the function call, the caller starts a new wave using a Wave-Advance.

2.2.5 *Memory Ordering*. Enforcing imperative language memory semantics is one of the key challenges that has prevented dataflow processing from

Fig. 5. Program order. The dashed line represents an implicit potential data dependence between the store and load instructions that conventional dataflow instruction sets have difficulty expressing. Without the dependence, the dataflow graph provides no ordering relationship between the memory operations.

becoming a viable alternative to the von Neumann model. Since dataflow ISAs only enforce the static data dependences in a program's dataflow graph, they have no mechanism ensuring that memory operations occur in program order. Figure 5 shows a dataflow graph that demonstrates the dataflow memory ordering problem. In the graph, the load must execute after the store to ensure correct execution, should the two memory addresses be identical. However, the dataflow graph does not express this implicit dependence between the two instructions (the dashed line). WaveScalar must provide an efficient mechanism to encode this implicit dependence in order to support imperative languages.

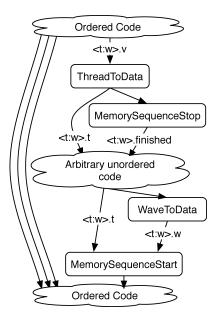

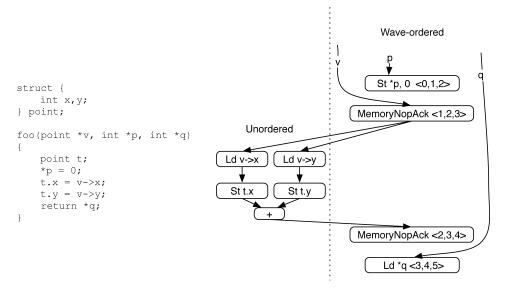

Wave-ordered memory solves the dataflow memory ordering problem, using the waves defined in Section 2.2.3. Within each wave, the compiler annotates memory access instructions to encode the ordering constraints between them. Since wave numbers increase as the program executes, they provide an ordering of the executing waves. Taken together, the coarse-grain ordering between waves (via their wave numbers), combined with the fine-grain ordering within each wave, provides a total order on all the memory operations in the program.

This section presents wave-ordered memory. Once we have more fully described waves and discussed the annotation scheme for operations within a wave, we describe how the annotations provide the necessary ordering. Then we briefly discuss an alternative solution to the dataflow memory ordering problem.

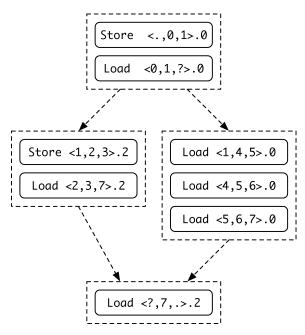

—Wave-ordering annotations. Wave-ordering annotations order the memory operations within a single wave. The annotations must guarantee two properties. Firstly, they must ensure that the memory operations within a wave execute in the correct order. Wave-ordered memory achieves this by giving each memory operation in a wave a *sequence number*. Sequence numbers increase on all paths through a wave, ensuring that if one memory operation has a larger

Fig. 6. Simple wave-ordered annotations. The three memory operations must execute in the order shown. Predecessor, sequence, and successor numbers encode the ordering constraints. The "." symbols indicate that operations 0 and 2 are the first and last operations, respectively, in the wave.

sequence number than another, the one with the larger number comes later in the program order. Figure 6 shows a very simple series of memory operations and their annotations. The sequence number is the second of the three numbers in angle brackets.

Secondly, wave-ordered memory must detect when all previous memory operations that will execute have done so. In the absence of branches, this detection is simple: Since all the memory operations in a wave will eventually execute, the memory system simply waits for all memory operations with lower sequence numbers to complete. Control flow complicates this method because it allows some of the memory operations to execute (those on taken paths) while others do not (those on the nontaken paths). To accommodate, wave-ordered memory must distinguish between operations that take a long time to fire and those that never will. To ensure that all memory operations on the correct path are executed, each memory operation also carries the sequence number of its previous and subsequent operations in the program order. Figure 6 includes these annotations as well. The predecessor number is the first number between the brackets, and the successor number is the last. For instance, the store in the figure is preceded by a load with sequence number 0 and followed by a load with sequence number 2, so its annotations are < 0, 1, 2 >. The "." symbols indicate that there is no predecessor of operation 0 and no successor of operation 2.

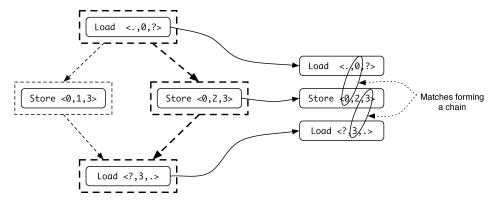

At branch (join) points, the successor (predecessor) number is unknown at compile time because control may take one of two paths. In these cases a "wild-card" symbol "?" takes the place of the successor (predecessor) number. The lefthand portion of Figure 7 shows a simple IF-THEN-ELSE control flow graph that demonstrates how the wildcard is applied; the righthand portion depicts how memory operations on the taken path are sequenced, described next.

Intuitively, the annotations allow the memory system to "chain" memory operations together. When the compiler generates and annotates a wave, there are many potential chains of operations through the wave, but only one chain (i.e., one control path) executes each time the wave executes (i.e., during one dynamic instance of the wave). For instance, the right side of Figure 7 shows the sequence of operations along one path through the code on the left. From one operation to the next, either the predecessor and sequence numbers, or the successor and sequence numbers match (the ovals in the figure).

In order for the chaining to be successful, the compiler must ensure that there is a complete chain of memory operations along every path through a

Fig. 7. Wave-ordering and control. Dashed boxes and lines denote basic blocks and control paths. The righthand-side of the figure shows the instructions that actually execute when control takes the righthand path (bold lines and boxes) and the matches between their annotations that define program order.

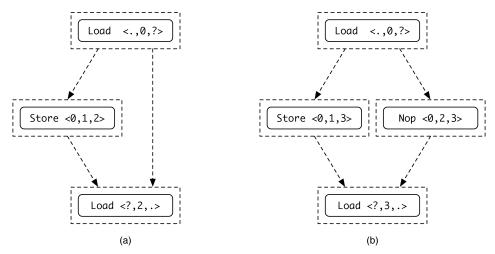

Fig. 8. Resolving ambiguity. In (a) chaining memory operations is impossible along the right-side path; (b) the addition of a Memory-Nop allows chaining.

wave. The chain must begin with an operation whose sequence number is 0 and end with successor number ".", indicating that there is no successor.

It is easy to enforce this condition on the beginning and end of the chain of operations, but ensuring that all possible paths through the wave are complete is more difficult. Figure 8(a) shows an example. The branch and join mean that instruction 0's successor and instruction 2's predecessor are both "?". As a result, the memory system cannot construct the required chain between operations 0 and 2 if control takes the righthand path. To create a chain, the compiler inserts a special Memory-Nop instruction between 0 and 2 on the righthand path (Figure 8(b)). The Memory-Nop has no effect on memory, but does send a request to the memory interface to provide the missing link in the chain. Adding Memory-Nops introduces a small amount of overhead, usually less than 3% of static instructions.

—Ordering rules. We can now demonstrate how WaveScalar uses wave numbers and the aforementioned annotations to construct a total ordering over all memory operations in a program. Figure 7 shows a simple example. Control takes the righthand path, resulting in three memory operations executed. At the right, ovals show the links between the three operations that form them into a chain. The general rule is that a link exists between two operations if the successor number of the first operation matches the sequence number of the second, or the sequence number of the first matches the predecessor number of the second.

Since the annotations only provide ordering with a wave, WaveScalar uses wave numbers to order the waves themselves. The WaveScalar processor must ensure that all the operations from previous waves complete before the operations in a subsequent wave can be applied to memory. Combining global interwave ordering with local intrawave ordering provides a total ordering on all operations in the program.

—*Expressing parallelism*. The basic version of wave-ordered memory described earlier can be easily extended to express parallelism between memory operations, allowing consecutive loads to execute in parallel or out-of-order.

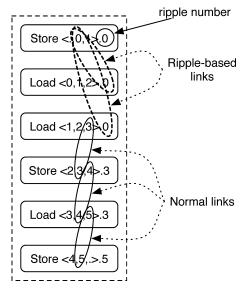

The annotations and rules define a linear ordering of memory operations, ignoring potential parallelism between loads. Wave-ordered memory can express this parallelism by providing a fourth annotation, called a *ripple number*. The ripple number of a store is equal to its sequence number. A load's ripple number points to the store that most immediately precedes it. To compute the ripple number for a load, the compiler collects the set of all stores that precede the load on any path through the wave. The load's ripple number is the maximum of the stores' sequence numbers. Figure 9 shows a sequence of load and store operations with all four annotations. Note that the predecessor numbers are still necessary to prevent a store from executing before the preceding loads have completed.

To accommodate ripples in the ordering rules, we allow a load to execute if it is next in the chain operations (as before), *or* if the ripple number of the load is less than or equal to the sequence number of a previously executed operation (a load or a store). Memory-Nops are treated like loads.

Figure 9 shows the two different types of links that can allow an operation to fire. The solid ovals between the bottom four operations are similar to those in Figure 7. The top two dashed ovals depict ripple-based links that allow the two loads to execute in either order or in parallel.

Figure 10 contains a more sophisticated example. If control takes the right-side branch, loads 1 and 4–6 can execute in parallel once store 0 has executed because they all have ripple numbers of 0. Load 7 must wait for one of loads 4–6 execute because the ripple number of operation 7 is 2 and loads 4–6 all have sequence numbers greater than 2. If control takes the lefthand branch, loads 3 and 7 can execute as soon as store 2 has executed.

Wave-ordered memory can express parallelism among load and store operations that a conventional out-of-order processor would discover by speculatively assuming memory independence [Chrysos and Emer 1998]. The speculative

Fig. 9. Simple ripples. A single wave containing a single basic block. The ripple annotations allow loads 1 and 2 to execute in either order or in parallel, while the stores must wait for all previous loads and stores to complete. Ovals depict the links formed between operations.

Fig. 10. Ripples and control. Branches make ripple behavior more complicated. If control takes the righthand path, Loads 1 and 4–6 can execute in any order, but Load 7 must wait for an operation with a sequence number greater than 2.

approach can also uncover some paralellism that wave-ordered memory cannot express (e.g., the compiler may be unable to prove that two stores are independent when they actually are). However, nothing in the WaveScalar instruction set or execution model prevents a WaveScalar processor from speculatively issuing memory operations and using the wave-ordering information to catch and correct mispeculations. Our implementation does not currently speculate.

2.2.6 Other Approaches. Wave-ordered memory is not the only way to provide the required memory ordering. Researchers have proposed an alternative scheme that makes implicit memory dependences explicit by adding a dataflow edge between each memory operation and the next [Beck et al. 1991; Budiu et al. 2004]. While this "token-passing" scheme is simple, it does not perform as well as wave-ordered memory; our experiments have found that wave-ordered memory expresses twice as much memory parallelism as token passing [Swanson 2006].

Despite this, token passing is very useful in some situations because it gives the programmer or compiler complete control over memory ordering. If very good memory aliasing is available, the programmer or compiler can express parallelism directly by judiciously placing dependences only between those memory operations that must actually execute sequentially. WaveScalar provides a simple token-passing facility for just this purpose (Section 6).

Previous dataflow machines have also provided two memory structures, I-structures and M-structures, intended to support functional programming languages. These structures combine memory ordering with synchronization.

—*I-structures*. Functional languages initialize variables when they are declared and disallow modifying their values. This eliminates the possibility of read-after-write data hazards. The variable always contains the correct value, so any read is guaranteed to see it. Dataflow language designers recognized that this approach restricts parallelism because an array must be completely initialized before its elements can be accessed. Ideally, one thread could fill-in the array, while another accesses the initialized elements.

Dataflow languages such Id [Nikhil 1990] and SISAL [Feo et al. 1995] provide this ability with I-structures [Arvind et al. 1989]. I-structures are write-once memory structures. When a program allocates an I-structure, it is *empty* and contains no value. A program can write, or fill-in, an I-structure (at most) once. Reading from an empty I-structure blocks until the I-structure is full. Reading from a full I-structure returns the value it holds. In the array example given before, one thread allocates an array of I-structures and starts filling them in. The second thread can attempt to read entries of the array, but will block if it tries to access an empty I-structure.

—*M-structures*. M-structures [Barth et al. 1991] provide checkin/checkout semantics for variables. Reading from a full M-structure removes the value, and a write fills the value back in. Attempting to read from an empty M-structure blocks until the value is returned.

A typical example of M-structures in action is a histogram. Each bucket is an M-structure, and a group of threads adds elements to the buckets concurrently.

Since addition is commutative, the order of updates is irrelevant, but they must be sequentialized. M-structures provide precisely the necessary semantics.

#### 2.3 Discussion

The WaveScalar instruction set that this section describes is sufficient to execute single-threaded applications written in conventional imperative programming languages. The instruction set is slightly more complex than a conventional RISC ISA, but we have not found the complexity difficult for the programmer or the compiler to handle.

In return for the complexity, WaveScalar provides three significant benefits. First, wave-ordered memory allows WaveScalar to efficiently provide the semantics that imperative languages require and to express parallelism among load operations. Second, WaveScalar can express instruction-level parallelism explicitly, while still maintaining these conventional memory semantics. Third, WaveScalar's execution model is distributed. Only instructions that must pass each other data communicate. There is no centralized control point.

In the next section we describe a microarchitecture that implements the WaveScalar ISA. We find that in addition to increasing instruction-level parallelism, the WaveScalar instruction set allows the microarchitecture to be substantially simpler than a modern out-of-order superscalar.

#### 3. A WAVECACHE ARCHITECTURE FOR SINGLE-THREADED PROGRAMS

WaveScalar's overall goal is to enable an architecture that avoids the scaling problems described in the Introduction. With the decentralized WaveScalar dataflow ISA in hand, our task is to develop a decentralized, scalable architecture to match. In addition to the scaling challenges, this architecture also must address additional challenges specific to WaveScalar. In particular, it must efficiently implement the dataflow firing rule and provide storage for multiple (perhaps many) instances of data values with different tags. It must also provide an efficient hardware implementation of wave-ordered memory.

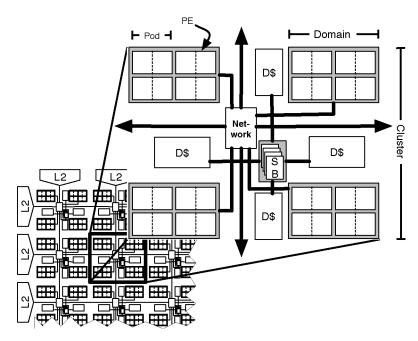

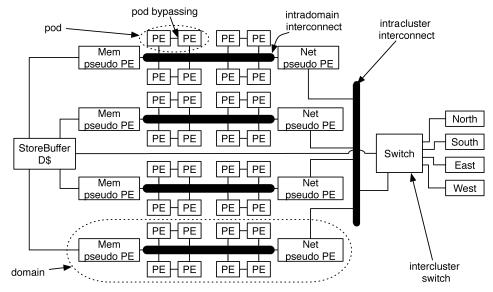

This section describes a tile-based WaveScalar architecture, called the *WaveCache*, that addresses these challenges. The WaveCache comprises everything, except main memory, required to run a WaveScalar program. It contains a scalable grid of simple, identical dataflow processing elements that are organized hierarchically to reduce operand communication costs. Each level of the hierarchy uses a separate communication structure: high-bandwidth, low-latency systems for local communication, and slower, narrower communication mechanisms for long-distance communication.

As we will show, the resulting architecture directly addresses two of the challenges we outlined in the Introduction. First, the WaveCache contains no long wires. In particular, as the size of the WaveCache increases, the length of the longest wires does not. Second, the WaveCache architecture scales easily from small designs suitable for executing a single thread to much larger designs suited to multithreaded workloads (See Section 5). The larger designs contain more tiles, but the tile structure, and therefore the overall design complexity, does not change. The final challenge mentioned in the Introduction, that of defect- and fault-tolerance, is the subject of ongoing research. The WaveCache's

Fig. 11. The WaveCache. The hierarchical organization of the microarchitecture of the WaveCache.

decentralized, uniform structure suggests that it would be easy to disable faulty components to tolerate manufacturing defects.

We begin by summarizing the WaveCache's design and operation at a high level in Section 3.1. Next, Sections 3.2 to 3.6 provide a more detailed description of its major components and how they interact. Section 3.7 describes a synthesizable RTL model that we use in combination with simulation studies to provide the specific architectural parameters for the WaveCache we describe. Finally, Section 3.8 describes other processor designs that share many of WaveScalar's goals. Section 4 evaluates the design in terms of performance and the amount of area it requires.

# 3.1 WaveCache Architecture Overview

Several recently proposed architectures, including WaveCache, take a tile-based approach to addressing the scaling problems outlined in the Introduction [Nagarajan et al. 2001; Sankaralingam et al. 2003; Lee et al. 1998; Mai et al. 2000; Goldstein and Budiu 2001; Budiu et al. 2004]. Instead of designing a monolithic core that comprises the entire die, tiled processors cover the die with hundreds or thousands of identical tiles, each of which is a complete, though simple, processing unit. Since they are less complex than the monolithic core and replicated across the die, tiles more quickly amortize design and verification costs. Tiled architectures also generally compute under decentralized control, contributing to shorter wire lengths. Finally, they can be designed to tolerate manufacturing defects in some portion of the tiles.

In the WaveCache, each tile is called a *cluster* (see Figure 11). A cluster contains four identical *domains*, each with eight identical processing elements

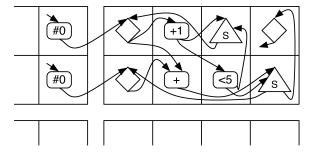

Fig. 12. Mapping instruction into the WaveCache. The loop in Figure 3(c) mapped onto two WaveCache domains. Each large square is a processing element.

(PEs). In addition, each cluster has a four-banked L1 data cache, wave-ordered memory interface hardware, and a network switch for communicating with adjacent clusters.

From the programmer's perspective, every static instruction in a WaveScalar binary has a dedicated processing element. Clearly, building an array of clusters large enough to give each instruction in an entire application its own PE is impractical and wasteful, so in practice, we dynamically bind multiple instructions to a fixed number of PEs, each of which can hold up to 64 instructions. Then, as the working set of the application changes, the WaveCache replaces unneeded instructions with newly activated ones. In essence, the PEs *cache* the working set of the application, hence the WaveCache moniker.

Instructions are mapped to and placed in PEs dynamically as a program executes. The mapping algorithm has two, often conflicting, goals: to place dependent instructions near each other (e.g., in the same PE) so as to minimize producer-consumer operand latency, and to spread independent instructions out across several PEs to exploit parallelism. Figure 12 illustrates how the WaveScalar program in Figure 3(c) can be mapped into two domains in the WaveCache. To minimize operand latency, the entire loop body (i.e., everything but the Const instructions that initiates the loop) has been placed in a single domain.

A processing element's chief responsibilities are to implement the dataflow firing rule and execute instructions. Each PE contains a functional unit, specialized memories to hold operands, and logic to control instruction execution and communication. It also contains buffering and storage for several different static instructions. A PE has a five-stage pipeline, with bypass networks that allow back-to-back execution of dependent instructions at the same PE. Two aspects of the design warrant special notice. First, it avoids the large, centralized associative tag-matching store found on some previous dataflow machines [Gurd et al. 1985]. Second, although PEs dynamically schedule execution, the scheduling hardware is dramatically simpler than a conventional dynamically scheduled processor. Section 3.2 describes the PE design in more detail.

To reduce communication costs within the grid, PEs are organized hierarchically along with their communication infrastructure (Figure 11). They are first coupled into *pods*; PEs within a pod snoop each other's ALU bypass networks

and share instruction scheduling information, and therefore achieve the same back-to-back execution of dependent instructions as a single PE. The pods are further grouped into domains; within a domain, PEs communicate over a set of pipelined buses. The four domains in a cluster communicate over a local switch. At the top level, clusters communicate over an on-chip interconnect built from the network switches in the clusters.

PEs access memory by sending requests to the memory interface in their local cluster. If possible, the local L1 cache provides the data. Otherwise, it initiates a conventional cache-coherence request to retrieve the data from the L2 cache (located around the edge of the array of clusters, along with the coherence directory) or L1 cache that currently owns the data.

A single cluster, combined with an L2 cache and traditional main memory, is sufficient to run any WaveScalar program, albeit with a possibly high Wave-Cache miss rate as instructions are swapped in and out of the small number of available PEs. To build larger and higher-performing machines, multiple clusters are connected by an on-chip network. A traditional directory-based MESI protocol maintains cache coherence.

## 3.2 The PE

At a high level, the structure of a PE pipeline resembles a conventional five-stage, dynamically scheduled execution pipeline. The biggest difference between the two is that the PE's execution is entirely data-driven. Instead of executing instructions provided by a program counter, as found on von Neumann machines, values (i.e., tokens) arrive at a PE destined for a particular instruction. The arrival of all of an instruction's input values triggers its execution: the essence of dataflow execution.

Our main goal in designing the PE was to meet our cycle-time goal while still allowing dependent instructions to execute on consecutive cycles. Pipelining was relatively simple. Back-to-back execution, however, was the source of significant complexity.

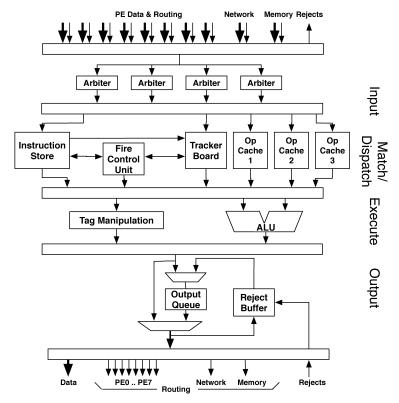

The PE's pipeline has five stages (see Figure 13):

- (1) *Input*. At the INPUT stage, operand messages arrive at the PE either from itself or another PE. The PE may reject messages if more than three arrive in one cycle; the senders then retry on a later cycle.

- (2) *Match*. During Match, operands enter the *matching table*. The matching table contains a tracker board and operand caches. It determines which instructions are ready to fire and issues eligible instructions by placing their matching table index into the instruction scheduling queue.

- (3) *Dispatch*. At the Dispatch stage, the PE selects an instruction from the scheduling queue, reads its operands from the matching table, and forwards them to Execute. If the destination of the dispatched instruction is local, this stage speculatively issues the consumer instruction to the scheduling queue.

- (4) *Execute*. The EXECUTE stage executes an instruction. Its result goes to the output queue and/or the local bypass network.

Fig. 13. PE block diagram. The processing element's structure by pipeline stage. Note that the block at the end of output is the same as the block at the start of input, since wire delay is spread between the two stages.

(5) *Output*. An instruction output is sent to its consumer instructions via the intradomain network during the Output stage. Consumers may be at this PE or a remote PE.

An instruction store holds the decoded instructions that reside at a PE. To keep it single-ported, the RTL design divides it into several small SRAMs, each holding the decoded information needed at a particular stage of the pipeline. The instruction store comprises about 33% of the PE's area.

The matching table handles instruction input matching. Implementing this operation cost-effectively is essential to an efficient dataflow machine. The key challenge in designing WaveScalar's matching table is emulating a potentially infinite table with a much smaller physical structure. This problem arises because WaveScalar is a dynamic dataflow architecture with no limit on the number of dynamic instances of a static instruction with unconsumed inputs. We use a common dataflow technique [Gurd et al. 1985; Shimada et al. 1986] to address this challenge: The matching table is a specialized cache for a larger, in-memory matching table. New tokens are stored in the matching cache. If a token resides there for a sufficiently long time, another token may arrive that hashes to the same location. In this case, the older token is sent to the matching table in memory.

Fig. 14. The flow of operands through the PE pipeline and forwarding networks.

The matching table is separated into three columns, one for each potential instruction input (certain WaveScalar instructions, such as data steering instructions, can have three inputs.)<sup>2</sup> Each column is divided into four banks to allow up to four messages to arrive at each cycle. Reducing the number of banks to two reduced performance by 5% on average and 15% for ammp. Increasing the number of banks to eight had negligible effect. In addition to the three columns, the matching table contains a tracker board which holds operand tags (wave number and consumer instruction number) and tracks which operands are present in each row of the matching table.

Since the matching table is a cache, we can apply traditional cache optimizations to reduce its miss rate. Our simulations show that two-way setassociativity increases performance over direct-mapped by 10% on average and reduces matching table misses (situations when no row is available for an incoming operand) by 41%. Four-way associativity provides less than 1% additional performance, hence the matching table is two-way. The matching table comprises about 60% of PE area.

To achieve good performance, PEs must be able to execute dependent instructions on consecutive cycles. When DISPATCH issues an instruction with a local consumer of its result, it speculatively schedules the consumer instruction to execute on the next cycle. The schedule is speculative because Dispatch cannot be certain that the dependent instruction's other inputs are available. If they are not, the speculatively scheduled consumer is ignored.

Figure 14 illustrates how instructions from a simple dataflow graph (on the lefthand-side of the figure) flow through the WaveCache pipeline. It also illustrates how the bypass network allows instructions to execute on consecutive cycles. In the diagram, X[n] is the nth input to instruction X. Five consecutive cycles are depicted; before the first of these, one input for each of instructions A and B has arrived and resides in the matching table, and the corresponding bits are also set in the tracker board. The tracker board also contains the tag (Thread-Id and Wave-Number) of the values in each occupied row. The "clouds"

$<sup>^2</sup>$ The third column is special and supports only single-bit operands. This is because three-input instructions in WaveScalar always have one argument which needs to be only a single bit. Other columns hold full 64-bit operands.

Fig. 15. The cluster interconnects. A high-level picture of a cluster illustrating the interconnect organization.

in the dataflow graph represent operands that were computed by instructions at other processing elements and have arrived via the input network.

- —*Cycle* 0: Operand *A*[0] arrives and INPUT accepts it (at left in Figure 14).

- — $Cycle\ 1$ : Match writes A[0] into the matching table and, because both its inputs are present, places A into the scheduling queue.

- —Cycle~2: DISPATCH chooses A for execution and reads its operands from the matching table. At the same time, it recognizes that A's output is destined for B. In preparation for this producer-consumer handoff, B is inserted into the scheduling queue.

- —*Cycle* 3: DISPATCH reads B[0] from the matching table. EXECUTE computes the result of A, which becomes B[1].

- —*Cycle* 4: Execute computes the result of instruction B, using B[0] from Dispatch and B[1] from the bypass network.

- —Cycle 5 (not shown): Output will send B's result to instruction Z.

The logic in Match and Dispatch is the most complex part of the entire Wave-Cache architecture, and most of it is devoted to logic that executes back-to-back dependent instructions within our cycle-time goal.

#### 3.3 The WaveCache Interconnect

The previous section described the execution resource of the WaveCache, namely, the PE. This section will detail how PEs on the same chip communicate. PEs send and receive data using a hierarchical on-chip interconnect (see Figure 15). There are four levels in this hierarchy: intrapod, intradomain, intracluster, and intercluster. While the purpose of each network is the same, that is, transmission of instruction operands and memory values, their designs

vary significantly. We will describe the salient features of these networks in the next four subsections.

3.3.1 PEs in a Pod. The first level of interconnect, the intrapod interconnect, enables two PEs to share scheduling hints and computed results. Merging a pair of PEs into a pod consequently provides lower-latency communication between them than that obtained by using the intradomain interconnect (described next). Although PEs in a pod snoop each other's bypass networks, the rest of their hardware remains partitioned, that is, they have separate matching tables, scheduling and output queues, etc.

The decision to integrate pairs of PEs together is a response to two competing concerns: We wanted the clock cycle to be short and instruction-to-instruction communication to take as few cycles as possible. To reach our cycle-time goal, the PE and the intradomain interconnect had to be pipelined. This increased average communication latency and reduced performance significantly. Allowing pairs of PEs to communicate quickly brought the average latency back down without significantly impacting cycle time. However, their tightly integrated design added significant complexity and took a great deal of effort to implement correctly. Integrating more PEs would increase complexity further, and our data showed that the additional gains in performance would be small.

3.3.2 The Intradomain Interconnect. PEs communicate with PEs in other pods over an intradomain interconnect. In addition to the eight PEs in the domain, the intradomain interconnect also connects two pseudo-PEs that serve as gateways to the memory system (the MEM pseudo-PE) and to other PEs on the chip (the Net pseudo-PE). The pseudo-PEs' interface to the intradomain network is identical to a normal PE's.

The intradomain interconnect is broadcast-based. Each of the eight PEs has a dedicated result bus that carries a single data result to the other PEs in its domain. Each pseudo-PE also has a dedicated output bus. PEs and pseudo-PEs communicate over the intradomain network using an Ack/Nack network.

- 3.3.3 The Intracluster Interconnect. The intracluster interconnect provides communication between the four domains' NET pseudo-PEs. It also uses an Ack/Nack network similar to that of the intra-domain interconnect.

- 3.3.4 The Intercluster Interconnect. The intercluster interconnect is responsible for all long-distance communication in the WaveCache. This includes operands traveling between PEs in distant clusters and coherence traffic for the L1 caches.

Each cluster contains an intercluster network switch which routes messages between six input/output ports: four of the ports lead to network switches in the four cardinal directions, one is shared among the four domains' NET pseudo-PEs, and one is dedicated to the store buffer and L1 data cache.

Each input/output port supports the transmission of up to two operands. Its routing follows a simple protocol: The current buffer storage state at each switch is sent to the adjacent switches, which receive this information one clock cycle later. Adjacent switches only send information if the receiver is guaranteed

Fig. 16. The microarchitecture of the store buffer.

to have space. The intercluster switch provides two virtual channels that the interconnect uses to prevent deadlock [Dally and Seitz 1987].

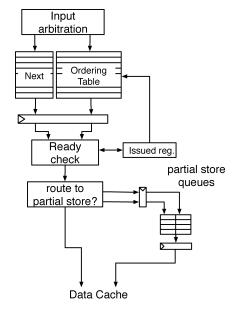

#### 3.4 The Store Buffer

The hardware support for wave-ordered memory lies in the WaveCache's store buffers. The store buffers, one per cluster, are responsible for implementing the wave-ordered memory interface that guarantees correct memory ordering. To access memory, processing elements send requests to their local store buffer via the Mem pseudo-PE in their domain. The store buffer will either process the request or direct it to another buffer via the intercluster interconnect. All memory requests for a single *dynamic* instance of a wave (e.g., an iteration of an inner loop), including requests from both local and remote processing elements, are managed by the same store buffer.

To simplify the description of the store buffer's operation, we denote  $\operatorname{pred}(R)$ ,  $\operatorname{seq}(R)$ , and  $\operatorname{succ}(R)$  as the wave-ordering annotations for a request R. We also define  $\operatorname{next}(R)$  to be the sequence number of the operation that actually follows R in the current instance of the wave. Specifically,  $\operatorname{next}(R)$  is either determined directly from  $\operatorname{succ}(R)$  or calculated by the wave-ordering hardware if  $\operatorname{succ}(R)$  is "?".

The store buffer (see Figure 16) contains four major microarchitectural components: an *ordering table*, a *next-request table*, an *issued register*, and a collection of *partial store queues*. Store buffer requests are processed in three pipeline stages: Memory-Input writes newly arrived requests into the ordering and next-request tables. Memory-Schedule reads up to four requests (one from each of the four banks) from the ordering table and checks to see if they are ready to issue. Memory-Output dispatches memory operations that can fire to the cache

or to a partial-store queue (described to follow). We detail each pipeline stage of this memory interface to next.

Memory-Input accepts up to four new memory requests per cycle. It writes the address, operation, and data (if available in the case of stores) into the ordering table at the index seq(R). If succ(R) is defined (i.e., not "?"), the entry in the next-request table at location seq(R) is updated to succ(R). If pred(R) is defined, the entry in the next-request table at location pred(R) is set to seq(R).

Memory-Schedule maintains the issued register which points to the subsequent memory operations to be dispatched to the data cache. It uses this register to read four entries from the next-request and ordering tables. If any memory ordering links can be formed (i.e., next-request table entries are not empty), the memory operations are dispatched to Memory-Output and the issued register is advanced. The store buffer supports the decoupling of store data from store addresses. This is done with a hardware structure called a partial-store queue, described next. The salient point for Memory-Schedule, however, is that Stores are sent to Memory-Output even if their data has not yet arrived.

Partial-store queues take advantage of the fact that store addresses can arrive significantly before their data. In these cases, a partial-store queue stores all operations to the same address. These operations must wait for the data to arrive, but operations to other addresses may proceed. When their data finally arrives, all operations in the partial-store queue can be applied in quick succession. Each WaveScalar store buffer contains two partial-store queues.

Memory-Output reads and processes dispatched memory operations. Four situations can occur: (1) The operation is a load or a store with its data present. The memory operation proceeds to the data cache; (2) the operation is a load or a store and a partial-store queue exists for its address. The memory operation is sent to the partial-store queue; (3) the operation is a store, its data has not yet arrived, and no partial-store queue exists for its address. A free partial-store queue is allocated and the store is sent to it; (4) the operation is a load or a store, but no free partial-store queue is available or its partial-store queue is full. The memory operation remains in the ordering table and the issued register is rolled back. The operation will reissue later.

# 3.5 Caches

The rest of the WaveCache's memory hierarchy comprises a 32KB, four-way set-associative L1 data cache at each cluster, and a 16MB L2 cache that is distributed along the edge of the chip (16 banks in a 4x4 WaveCache). A directory-based MESI coherence protocol keeps the L1 caches consistent. All coherence traffic travels over the intercluster interconnect.

The L1 data cache has a three-cycle hit delay. The L2's hit delay is 14–30 cycles, depending upon the address and the distance to the requesting cluster. Main memory latency is modeled at 200 cycles.

## 3.6 Placement

Placing instructions carefully into the WaveCache is critical to good performance because of the competing concerns we mentioned earlier. Instructions'

ACM Transactions on Computer Systems, Vol. 25, No. 2, Article 4, Publication date: May 2007.

proximity determines the communication latency between them, arguing for tightly packing instructions together. On the other hand, instructions that can execute simultaneously should not end up at the same processing element because competition for the single functional unit will serialize them.

We continue to investigate the placement problem, and details of our investigation, the tradeoffs involved, and a placement's effects on performance are available in Mercaldi et al. [2006a, 2006b]. Here, we describe the approach we used for the studies in this article.

The placement scheme has a compile-time and a runtime component. The compiler is responsible for grouping instructions into segments. At runtime, a whole segment of instructions will be placed at the same PE. Because of this, the compiler tries to group instructions into the same segment if these instructions are not likely to execute simultaneously but share operands, and therefore can utilize the fast local bypass network available inside of each PE. The algorithm we use to form segments is a depth-first traversal of the dataflow graph.

At runtime, the WaveCache loads a segment of instructions when an instruction that is not mapped into the WaveCache needs to execute. As previously discussed, the entire segment is mapped to a single PE. Because of the ordering that the compiler used to generate the segments, they will usually be dependent on one another. As a result, they will not compete for execution resources, but instead will execute on consecutive cycles. The algorithm fills all the PEs in a domain, and then all the domains in a cluster, before moving on to the next cluster. It fills clusters by "snaking" across the grid, moving from left-to-right on even rows and right-to-left on odd rows.

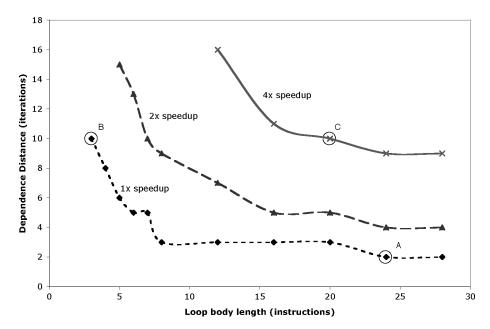

This placement scheme does a good job of scheduling for minimal execution resource contention and communication latency. However, a third factor, the so-called "parallelism explosion," can also have a strong effect on performance in dataflow systems. The parallelism explosion occurs when part of an application (e.g., the index computation of an inner loop) runs ahead of the rest of the program, generating a vast number of tokens that will not be consumed for a long time. These tokens overflow the matching table and degrade performance. We use a well-known dataflow technique, k-loop bounding [Culler 1990], to restrict the number iterations k that can be executing at one time. We tune k for each application, and for the applications we study, it is between two and five.

## 3.7 The RTL Model

To explore the area, speed, and complexity implications of the WaveCache architecture, we have developed a synthesizable RTL model of the components described earlier. We use the RTL model, combined with detailed architectural simulation, to tune the WaveCache's parameters and make tradeoffs between performance, cycle time, and silicon area. All the specific parameters of the architecture (e.g., cache sizes, bus widths, etc.) reflect the results of this tuning process. The design we present is a WaveCache appropriate for general-purpose processing in 90nm technology. Other designs targeted at specific workloads or future process technologies would differ in the choice of particular parameters,

|                     | _            |

|---------------------|--------------|

|                     | Fraction of  |

| Component           | Cluster Area |

| PE stages           |              |

| Input               | 0.9%         |

| Match               | 43.3%        |

| DISPATCH            | 0.4%         |

| Execute             | 1.8%         |

| Оитрит              | 1.3%         |

| instruction store   | 23.2%        |

| PE total            | 71%          |

| Domain overhead     | 7.4%         |

| Intercluster        | 0.9%         |

| interconnect switch |              |

| Storebuffer         | 6.2%         |

| L1 cache            | 14.5%        |

Table I. A Cluster's Area Budget

A breakdown of the area required for a cluster. Most of the area is devoted to processing resources.

but the overall structure of the design would remain the same. A thorough discussion of the RTL design and the tuning process is beyond the scope of this article (but can be found in Swanson et al. [2006]). Here, we summarize the methodology and timing results.

We derive our results with the design rules and recommended tool infrastructure of the Taiwan Semiconductor Manufacturing Company's TSMC Reference Flow 4.0 [TSMC 2007], which is tuned for 130nm and smaller designs (we use 90nm). By using these up-to-date specifications, we ensure, as best as possible, that our results scale to future technology nodes. To ensure that our measurements are reasonable, we follow TSMC's advice and feed the generated netlist into Cadence Encounter for floorplanning and placement, and then use Cadence NanoRoute for routing [Cadence 2007]. After routing and RC extraction, we measure the timing and area values.

According to the synthesis tools, our RTL model meets our timing goal of a 20 FO4 cycle time ( $\sim 1 \mathrm{GHz}$  in 90nm). The cycle time remains the same, regardless of the size of the array of clusters. The model also provides detailed area measurements for the WaveCache's components. Table I shows a breakdown of area within a single cluster. The ratios for an array of clusters are the same.

In the next section, we place the WaveCache in context relative to other tiled architectures. Then, in Section 4 we evaluate WaveCache's performance on single-threaded applications and compare this as well as its area requirements with a conventional superscalar processor.

#### 3.8 Other Tiled Architectures

The WaveCache hardware design described in Sections 3 and 5 is a tiled architecture. Broadly speaking, a tiled architecture is a processor design that uses an array of basic building blocks of silicon to construct a larger processor.

Tiled architectures provide three advantages over traditional monolithic designs. First, they reduce design complexity by emphasizing design reuse.

$ACM\ Transactions\ on\ Computer\ Systems,\ Vol.\ 25,\ No.\ 2,\ Article\ 4,\ Publication\ date:\ May\ 2007.$

WaveScalar exploits this principle at several levels (PE, domain, and cluster). Second, tiled designs seek to avoid long wires. In modern technology, wire delay dominates the cost of computation. Wires in most tiled architectures span no more than a single tile, ensuring that wire length does not increase with the number of tiles. Finally, tiled architectures seek to be scalable. An ideal tiled architecture would scale to any number of tiles, both in terms of functional correctness and in terms of performance.

Several research groups have proposed tiled architectures with widely varying tile designs. Smart Memories [Mai et al. 2000] provides multiple types of tiles (e.g., processing elements and reconfigurable memory elements). This approach allows greater freedom in configuring an entire processor, since the mix of tiles can vary from one instantiation to the next, perhaps avoiding the difficulties in naive scaling that we found in our study.

The TRIPS [Nagarajan et al. 2001; Sankaralingam et al. 2003] processor uses dataflow ideas to build a hybrid von Neumann/dataflow machine. It uses a program counter to guide execution, but instead of moving from one instruction to the next, the TRIPS PC selects *frames* (similar to hyperblocks [Mahlke et al. 1992]) of instructions for execution in an array of 16 processing elements that make up a TRIPS processor.

Despite high-level similarities between waves and frames and the WaveScalar and TRIPS PE designs, the two architectures are quite different. In TRIPS, a register file at the top of the array holds values that pass from one frame to another. Each TRIPS PE can hold multiple instructions, so each PE requires multiple input buffers. However, execution follows the static dataflow model, making tag matching logic unnecessary.

Using dataflow execution within a von Neumann processor is the same approach taken by out-of-order superscalars, but the TRIPS design avoids the long wires and broadcast structures that make conventional out-of-order processors nonscalable. However, because it uses a program counter to select frames of instructions for execution, TRIPS must speculate aggressively. Mapping a frame of instructions onto the PE array takes several cycles, so the TRIPS processor speculatively maps frames onto the PEs ahead of time. WaveScalar does not suffer from this problem because its dynamic dataflow execution model allows instructions to remain in the grid for many executions, obviating the need for speculation. The disadvantage of WaveScalar's approach is the need for complex tag-matching hardware to support dynamic dataflow execution

The two projects also have much in common. Both take a hybrid static/dynamic approach to scheduling instruction execution by carefully placing instructions in an array of processing elements and then allowing execution to proceed dynamically. This places both architectures between dynamic out-of-order superscalar designs and statically scheduled VLIW machines. Those designs have run into problems because dynamic scheduling hardware does not scale and by nature, static scheduling is conservative. A hybrid approach will be necessary, but it is as yet unclear whether either WaveScalar or TRIPS strikes the optimal balance.

WaveScalar and TRIPS also take similar approaches to ordering memory operations. TRIPS uses load/store IDs (LSIDs) [Smith et al. 2006] to order memory

| WaveCache Capacity | $2K(WC1\times1)$ or $8K(WC2\times2)$ static instructions (64/PE) |

|--------------------|------------------------------------------------------------------|

| PEs per Domain     | 8 (4 pods); 1 FPU/domain                                         |

| PE Input Queue     | 16 entries, 4 banks (1KB total); 32 cycle miss penalty           |

| PE Output Queue    | 4 entries, 2 ports (1r, 1w)                                      |

| PE Pipeline Depth  | 5 stages                                                         |

| Domains/Cluster    | 4                                                                |

| Network Switch     | 2-port, bidirectional                                            |

| Network Latency    | within Pod: 1 cycle                                              |

|                    | within Domain: 5 cycles                                          |

|                    | within Cluster: 9 cycles                                         |

|                    | Intercluster: $9 + \text{cluster dist.}$                         |

| L1 Caches          | 32KB, 4-way set-associative, 128B line,                          |